# MCP18480

## -48V Hot Swap Controller

#### **Features**

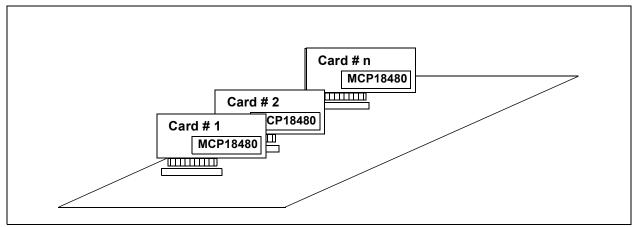

- Allows safe board removal and insertion from a live backplane

- Accurate (<1.5%) internal voltage reference for fault detection and precision timing

- · Programmable foldback current limiting

- Programmable circuit breaker current limiting

- · Auto restart option for all faults

- · Adjustable Undervoltage lockout thresholds

- · Adjustable Overvoltage protection threshold

- · Adjustable Power Good delay

- · Configurable Power Good output polarity

- · Low-side drive of an external N-channel FET

### **CMOS Technology**

- · High-Voltage Operation

- Temperature range: Industrial (I): -40°C to +85°C

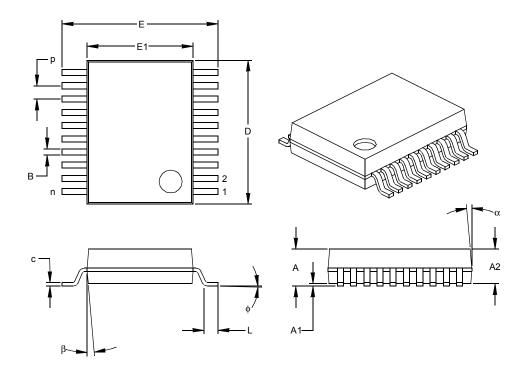

## **Packaging**

20-lead SSOP

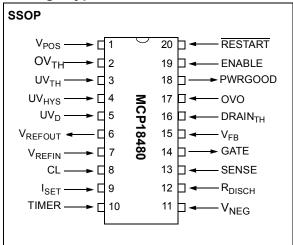

## Package Type

## **Description**

The MCP18480 is a Hot Swap controller that allows boards to be safely removed or inserted from an active backplane using -48V.

When PCBs are inserted into a live backplane, highpeak or transient currents from the source are generated due to the charging of the bypass capacitors on the supply. The high transient currents can destroy connectors and capacitors. The high inrush current can pull the input voltage BUS down and reset the system.

The MCP18480 solves this problem by controlling the slew rate of the backplane voltage to the board so that these transients are eliminated. This allows boards to be removed and inserted without causing damage to connector pins and input bulk capacitors, in addition to preventing false resets to the other boards on the backplane.

The MCP18480 can be used in applications in several areas including:

- · Telecom Line Cards

- · Network Switches

- Network Routers and Servers

- · Base Station Line Cards

- Power-Over-LAN

- Power-Over-MDI

- · IP Phone Switches/Routers

- · Mid-Span, Power-Over-MDI

Two forms of current limit are provided in the MCP18480. These are:

- Foldback

- · Circuit breaker

The foldback current-limiting circuit uses an external sense resistor and a voltage that is proportional to the external MOSFET's drain voltage. These are used to keep the MOSFET in its Safe Operating Area (SOA).

If the device remains in current limit for a programmed time period, the external N-channel FET is turned off. The option exists to configure the device to automatically restart after a programmed time delay. A programmable catastrophic current limit threshold shuts down the switch (circuit breaker) if excessive current is sensed due to a short-circuit condition.

Internal comparators are incorporated to add hysteresis for adjusting the Undervoltage Lockout (UVLO) threshold. The external N-channel MOSFET is turned on when the input is below the user-programmable, Overvoltage threshold and above the user-programmable, Undervoltage threshold.

The PWRGOOD pin indicates the status of the MCP18480 and is active when the device has completed power-up and the system is not in an Undervoltage, Overvoltage or current-limit condition.

PWRGOOD can be externally configured to either active-high or active-low to accommodate external circuitry (power supplies) that have either enabling logic.

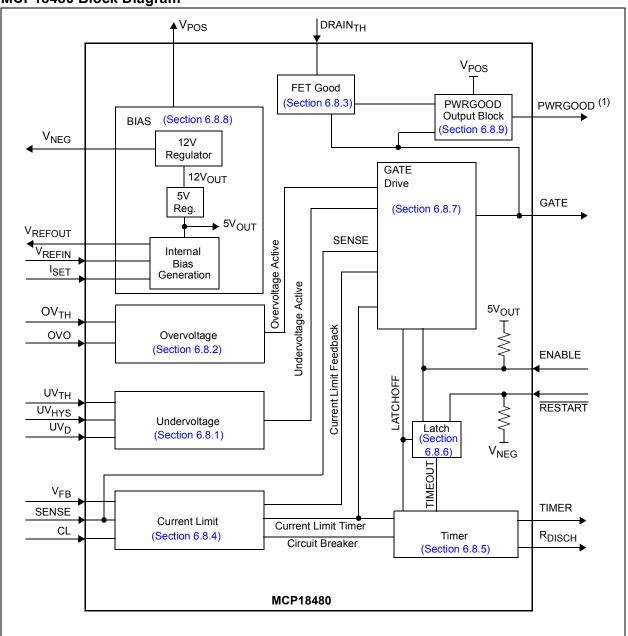

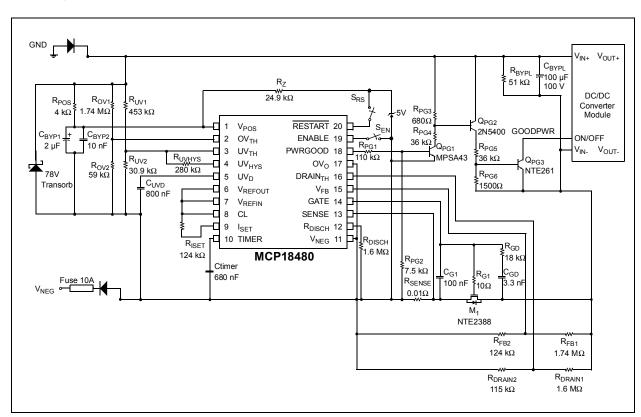

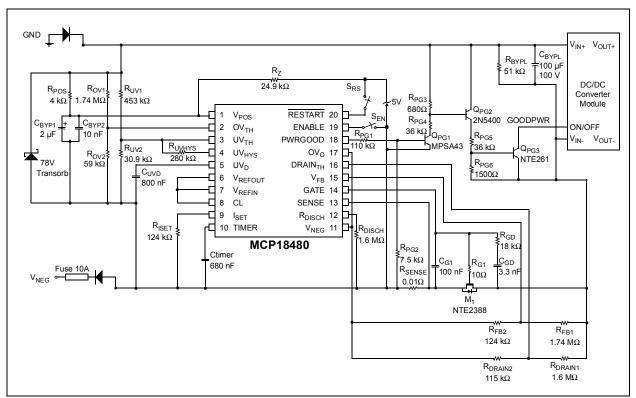

A block diagram of the MCP18480 is shown below.

## MCP18480 Block Diagram

**Note 1:** The PWRGOOD output pin can be either active-high or active-low. This polarity is determined by the voltage (either the level on the  $V_{REFIN}$  pin or level on the  $V_{NEG}$  pin) on the  $I_{SET}$  pin:

- Connecting the external  $R_{\mbox{\scriptsize ISET}}$  resistor to  $V_{\mbox{\scriptsize REFIN}}$  configures the PWRGOOD pin as active-low

- Connecting the external  $R_{\mbox{\scriptsize ISET}}$  resistor to  $V_{\mbox{\scriptsize NEG}}$  configures the PWRGOOD pin as active-high

## 1.0 ELECTRICAL CHARACTERISTICS

## **Absolute Maximum Ratings†**

| Ambient Temperature under bias –40 $^{\circ}\text{C}$ to +85 $^{\circ}\text{C}$                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                                                                                                                       |

| Voltage on $V_{\mbox{POS}}$ with respect to $V_{\mbox{NEG}}$ -0.3V to +15.0V                                                                                                            |

| Voltage on DV <sub>TH</sub> , UV <sub>TH</sub> , V <sub>FB</sub> , OVO and UV <sub>HYS</sub> pins with respect to V <sub>NEG</sub> V <sub>NEG</sub> – 0.3V to (V <sub>POS</sub> + 0.3V) |

| $\label{eq:voltage} \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                 |

|                                                                                                                                                                                         |

| Total Power Dissipation (Note 1)800 mW                                                                                                                                                  |

| Max. Current out of V <sub>NEG</sub> pin80 mA                                                                                                                                           |

| Max. Current into V <sub>POS</sub> pin50 mA                                                                                                                                             |

| Max. Output Current sunk by Gate pin80 mA                                                                                                                                               |

| Max. Output Current sunk by V <sub>REFOUT</sub> pin 5 mA                                                                                                                                |

| Max. Output Current sunk by any other                                                                                                                                                   |

| Output pin25 mA                                                                                                                                                                         |

| Max. Output Current sourced by Gate pin200 μA                                                                                                                                           |

| Max. Output Current sourced by V <sub>REFOUT</sub> pin5 mA                      |

|---------------------------------------------------------------------------------|

| Max. Output Current sourced by any other Output pin25 mA                        |

| Junction to Ambient, Θ <sub>JA</sub><br>(20 pin SSOP Package) Derating108.1°C/W |

| Junction to Case, $\Theta_{JC}$ (20 pin SSOP Package) Derating32.2°C/W          |

| Lead Temperature, Soldering, 10 seconds 300°C                                   |

| † Notice: Stresses above those listed under "Maximum                            |

those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at

**Note 1:** Power Dissipation is calculated as follows:  $P_{DIS} = V_{DD} \times \{I_{DD} - \Sigma \mid_{OH}\} + \Sigma \{(V_{DD} - V_{OH}) \times I_{OH}\} + \Sigma (V_{OL} \times I_{OL})$

## **DC CHARACTERISTICS**

Electrical Specifications: Unless otherwise specified, operating temperature:  $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$  (Industrial), Supply Current:  $5 \text{ mA} \le I_{POS} \le 25 \text{ mA}$ ,  $R_{ISET} = 125 \text{ k}\Omega$ ,  $C_{BYP} = 2 \text{ \muF}$ .

Param.

Parameter

Sym

Min

Typ (1)

Max

Units

Conditions

| Param.<br>No. | Parameter                                                      |         | Sym                 | Min                              | Typ <sup>(1)</sup>           | Max                              | Units | Conditions                    |

|---------------|----------------------------------------------------------------|---------|---------------------|----------------------------------|------------------------------|----------------------------------|-------|-------------------------------|

| MD001         | Current into shunt regulator                                   |         | I <sub>POS1</sub>   | 5                                |                              | 25                               | mA    | ENABLE pin = 5V               |

|               | that produces V <sub>POS</sub> of age that meets MD00 fication |         |                     | 5                                |                              | 25                               |       | ENABLE pin = V <sub>NEG</sub> |

| MD001A        | Regulated Output Vol<br>Differential of V <sub>POS</sub> to    |         | V <sub>POS</sub>    | 10.4                             | 12.0                         | 13.4                             | >     | See MD001                     |

| MD002         | V <sub>REFOUT</sub> pin output vo                              | oltage  | V <sub>REFOUT</sub> | 2.463                            | 2.5                          | 2.538                            | V     | Load = 50 μA                  |

| MD010         | V <sub>GATE</sub> pin output volta                             | age     | $V_{GATE}$          | V <sub>POS</sub> - 2             | V <sub>POS</sub> -1          | V <sub>POS</sub>                 | >     |                               |

| MD011         | Voltage on I <sub>SET</sub> pin                                |         | V <sub>ISET</sub>   | (V <sub>REFIN</sub> /2)-<br>0.02 | V <sub>REFIN</sub> /2        | (V <sub>REFIN</sub> /2)<br>+0.02 | >     |                               |

| MD012A        | Voltage on SENSE pi                                            |         | V <sub>SENSE</sub>  | 40                               | 50                           | 60                               | mV    | $V_{FB} = V_{NEG}$            |

| MD012B        | trigger current-limiting                                       |         |                     | 25                               | 31.0                         | 40                               | mV    | $V_{FB} = V_{NEG} + 0.25V$    |

| MD012C        |                                                                |         |                     | 7                                | 12                           | 17                               | mV    | $V_{FB} = V_{NEG} + 0.5V$     |

| MD013         | Undervoltage Thresho                                           | old     | UV <sub>TH</sub>    | V <sub>REFIN</sub><br>- 0.03     | $V_{REFIN}$                  | V <sub>REFIN</sub><br>+ 0.03     | ٧     |                               |

| MD014A        | Overvoltage<br>Threshold                                       | rising  | OV <sub>TH</sub>    | V <sub>REFIN</sub><br>- 0.05     | V <sub>REFIN</sub>           | V <sub>REFIN</sub><br>+ 0.05     | V     | V <sub>REFIN</sub> = 2.5V     |

| MD014B        |                                                                | falling | OV <sub>TH</sub>    | V <sub>REFIN</sub><br>- 0.035    | V <sub>REFIN</sub><br>- 0.02 | V <sub>REFIN</sub><br>- 0.005    | V     | V <sub>REFIN</sub> = 2.5V     |

| MD015         | DRAIN Pin Input Thre Voltage                                   | shold   | V <sub>DTH</sub>    | 90                               | 100                          | 130                              | mV    |                               |

Note 1: Data in the Typical ("Typ") column is based on characterization results at +25°C. This data is for design guidance only and is not tested.

- 2: Negative current is defined as current sourced by the pin.

- 3: All voltages are with respect to the V<sub>NEG</sub> pin voltage.

## **DC Characteristics (Continued)**

**Electrical Specification:** Unless otherwise specified, operating temperature:  $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$  (Industrial), Supply Current:  $5 \text{ mA} \le I_{POS} \le 25 \text{ mA}$ ,  $R_{ISET} = 125 \text{ k}\Omega$ ,  $C_{BYP} = 2 \mu\text{F}$

| Capp.y Ca     | 11011t. 0 1111 t = 120S = 2  | ,         | 120 1122, 0        | BAB - M.               |                    |                                                  |       |                                                                                     |

|---------------|------------------------------|-----------|--------------------|------------------------|--------------------|--------------------------------------------------|-------|-------------------------------------------------------------------------------------|

| Param.<br>No. | Paramete                     | er        | Sym                | Min                    | Typ <sup>(1)</sup> | Max                                              | Units | Conditions                                                                          |

| MD020         | DRAIN pin current            |           | I <sub>DRAIN</sub> | _                      | _                  | 0.1                                              | μΑ    | DRAIN <sub>TH</sub> pin = V <sub>NEG</sub>                                          |

| MD021         | SENSE pin current            |           | I <sub>SENSE</sub> | 1                      | _                  | 0.1                                              | μΑ    |                                                                                     |

| MD022         | GATE pin current             | Pull-up   | I <sub>GATE</sub>  |                        |                    |                                                  |       | SENSE pin = V <sub>NEG</sub><br>GATE pin = V <sub>NEG</sub> +4V                     |

| MD022A        |                              |           |                    | -30                    | -50                | -75                                              | μΑ    | V <sub>FB</sub> = V <sub>NEG</sub>                                                  |

| MD022B        |                              |           |                    | -9                     | -17                | -33                                              | μΑ    | $V_{FB} = V_{NEG} + 500 \text{ mV}$                                                 |

| MD022C        |                              | Pull-down | I <sub>GATE</sub>  | 31                     | 49                 | 72                                               | mA    | Any fault condition                                                                 |

| MD023         | UV <sub>D</sub> pin current  |           | $I_{UVD}$          | -7                     | -10                | -15                                              | μΑ    | UV <sub>TH</sub> < V <sub>REFIN</sub>                                               |

| MD024A        | TIMER pin current            | Pull-up   | I <sub>TIMER</sub> | -100                   | -160               | -200                                             | μΑ    | $R_{ISET}$ = 125 k $\Omega$ ,<br>V <sub>REFIN</sub> = 2.5V                          |

| MD024B        |                              | Pull-down |                    | 52                     | 78                 | 104                                              | nA    | $R_{ISET}$ = 125 k $\Omega$ ,<br>$V_{REFIN}$ = 2.5V<br>$R_{DISCH}$ = 1.6 M $\Omega$ |

| MD025         | I <sub>SET</sub> pin current |           | I <sub>ISET</sub>  | V <sub>ISET(MIN)</sub> | _                  | V <sub>ISET(MAX)</sub><br>R <sub>ISET(MIN)</sub> | Α     | See MD011                                                                           |

Note 1: Data in the Typical ("Typ") column is based on characterization results at +25°C. This data is for design guidance only and is not tested.

- 2: Negative current is defined as current sourced by the pin.

- 3: All voltages are with respect to the  $V_{\mbox{\scriptsize NEG}}$  pin voltage.

## **DC Characteristics (Continued)**

**Electrical Specifications:** Unless otherwise specified, operating temperature:  $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$  (Industrial), Supply Current: 5 mA  $\le$  I<sub>POS</sub>  $\le$  25 mA, R<sub>ISET</sub> = 125 kΩ, C<sub>BYP</sub> = 2 μF.

| Param # | Parameter                                                                                                            | Sym                | Min                  | Тур                   | Max              | Units | Conditions                                                             |

|---------|----------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-----------------------|------------------|-------|------------------------------------------------------------------------|

| MD030   | Input Low Voltage                                                                                                    | V <sub>IL</sub>    |                      |                       |                  |       |                                                                        |

| MD031   | ENABLE pin                                                                                                           |                    | $V_{NEG}$            | _                     | 8.0              | V     |                                                                        |

| MD032   | RESTART pin                                                                                                          |                    | V <sub>NEG</sub>     | _                     | 8.0              |       |                                                                        |

| MD040   | Input High Voltage                                                                                                   | V <sub>IH</sub>    |                      |                       |                  |       |                                                                        |

| MD041   | ENABLE pin                                                                                                           |                    | 2.0                  | _                     | 5.0              | V     |                                                                        |

| MD042   | RESTART pin                                                                                                          |                    | 2.0                  | 1                     | 5.0              | V     |                                                                        |

| MD050   | Internal Resistance on UV <sub>HYS</sub> pin                                                                         | R <sub>UVHYS</sub> | 500                  | 1200                  | 2100             | Ω     | V <sub>UVTH</sub> < V <sub>REFIN</sub> ,<br>I <sub>UVHYS</sub> = 30 μA |

|         |                                                                                                                      |                    | 50                   | 100                   |                  | МΩ    | V <sub>UVTH</sub> > V <sub>REFIN</sub> ,<br>I <sub>UVHYS</sub> = 30 μA |

|         | Input Leakage Current (Notes 2, 3)                                                                                   |                    |                      |                       |                  |       |                                                                        |

| MD060A  | $\ensuremath{OV_{TH}}, \ensuremath{UV_{TH}}, \ensuremath{V_{FB}}, \ensuremath{OVO}$ and $\ensuremath{UV_{HYS}}$ pins | I <sub>IL</sub>    | -1                   | _                     | +1               | μΑ    | V <sub>NEG</sub> ≤ V <sub>PIN</sub> ≤ 11V, Pin at high-impedance       |

| MD060B  | V <sub>REFIN</sub> , CL, SENSE, DRAIN <sub>TH</sub> ,<br>ENABLE and RESTART pins                                     |                    | _                    | _                     | ±1               | μΑ    | $V_{NEG} \le V_{PIN} \le 5V$ , Pin at hi-impedance                     |

| MD070   | Minimum current into ENABLE pin to disable MCP18480                                                                  | I <sub>EN</sub>    | _                    | 10                    | 30               | μΑ    | I <sub>POS</sub> = 5 mA,<br>ENABLE = 0.8V                              |

|         | Output Low Voltage                                                                                                   | $V_{OL}$           |                      |                       |                  |       |                                                                        |

| MD080   | PWRGOOD pin                                                                                                          |                    | 0                    | _                     | 0.4              | V     | I <sub>OL</sub> = 5 mA                                                 |

|         | Output High Voltage                                                                                                  | V <sub>OH</sub>    |                      | _                     |                  |       |                                                                        |

| MD090   | PWRGOOD pin                                                                                                          |                    | 0.8 V <sub>POS</sub> | 0.96 V <sub>POS</sub> | V <sub>POS</sub> | V     | $I_{OH}$ = 2 mA,<br>7 mA $\leq I_{POS} \leq$ 12 mA                     |

| MD100   | Offset Voltage at the internal comparator input that is connected to the CL pin.                                     | V <sub>CL</sub>    | -15                  | _                     | +15              | mV    | V <sub>FB</sub> = 0                                                    |

Note 1: All voltages are with respect to the V<sub>NEG</sub> pin voltage.

2: The leakage currents on the ENABLE and RESTART pins are strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as coming out of the pin.

## 1.1 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created using one of the following formats:

## 1.1.1 TIMING CONDITIONS

The temperature and voltages specified in Table 1-2 apply to all timing specifications, unless otherwise noted. Figure 1-1 specifies the load conditions for the timing specifications.

2. TppS

## TABLE 1-1: SYMBOLOGY

Invalid (Hi-impedance)

Low

1. TppS2ppS

| Т       |                                          |   |        |  |

|---------|------------------------------------------|---|--------|--|

| F       | Frequency                                | Т | Time   |  |

| E       | Error                                    |   |        |  |

| Lowerca | se letters (pp) indicate the device pin. |   |        |  |

| Upperca | se letters and their meanings:           |   |        |  |

| S       |                                          |   |        |  |

| F       | Fall                                     | Р | Period |  |

| FR      | Fast Ramp                                | R | Rise   |  |

| Н       | High                                     | V | Valid  |  |

## TABLE 1-2: AC TEMPERATURE AND VOLTAGE SPECIFICATIONS

|                           | Standard Operating Conditions (unless otherwise stated)            | 1 |

|---------------------------|--------------------------------------------------------------------|---|

| <b>AC CHARACTERISTICS</b> | Operating temperature: –40°C ≤ T <sub>A</sub> ≤ +85°C (industrial) |   |

|                           | Operating voltage VDD range as described in DC spec Section 1.0.   |   |

Ζ

Hi-impedance

FIGURE 1-1: Load Conditions for Device Timing Specifications.

## 1.2 Timing Diagrams and Specifications

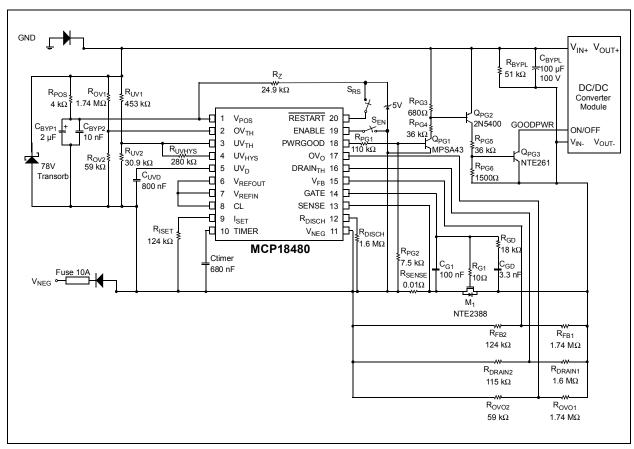

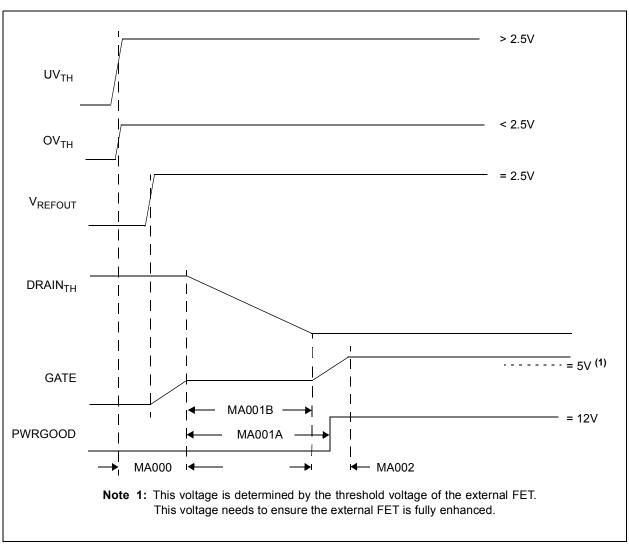

FIGURE 1-2: Startup Waveforms.

TABLE 1-3: STARTUP TIMING REQUIREMENTS

| Param.<br>No. | Parameter                                                                         | Sym                                     | Min | Тур  | Max | Units | Conditions |

|---------------|-----------------------------------------------------------------------------------|-----------------------------------------|-----|------|-----|-------|------------|

| MA000         | ${ m UV_{TH}/OV_{TH}}$ High ( ${ m V_{POS}}$ applied) to DRAIN $_{ m TH}$ falling | T <sub>UVOV</sub> H2 <sub>DTH</sub> F   | _   | 20.2 |     | ms    |            |

| MA001A        | DRAIN <sub>TH</sub> falling to PWRGOOD High                                       | T <sub>DTH</sub> F2 <sub>GATE</sub> PGH | _   | 19.3 | _   | ms    |            |

| MA001B        | DRAIN <sub>TH</sub> falling to GATE Fast Ramp                                     | T <sub>DTH</sub> F2 <sub>GATE</sub> FR  | _   | 13.1 | _   | ms    |            |

| MA002         | GATE Fast Ramp to external FET fully enhanced                                     | TGATEFR2FET <sub>E</sub>                | _   | 16.1 | _   | ms    |            |

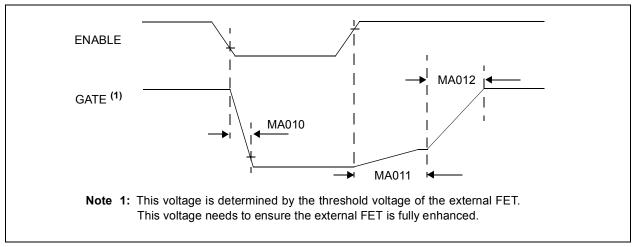

FIGURE 1-3: ENABLE-to-GATE Waveforms.

TABLE 1-4: ENABLE-TO-GATE TIMING REQUIREMENTS

| Param.<br>No. | Parameter                     | Sym                                     | Min | Тур  | Max | Units | Conditions |

|---------------|-------------------------------|-----------------------------------------|-----|------|-----|-------|------------|

| MA010         | ENABLE Low to GATE Low        | T <sub>EN</sub> L2 <sub>GATE</sub> L    | _   | 23.6 | _   | μs    |            |

| MA011         | ENABLE High to GATE Fast Ramp | T <sub>EN</sub> H2 <sub>GATE</sub> FR   | _   | 41   | _   | ms    |            |

| MA012         | GATE Fast Ramp to GATE High   | T <sub>GATE</sub> FR2 <sub>GATE</sub> H | 1   | 17.8 | _   | ms    |            |

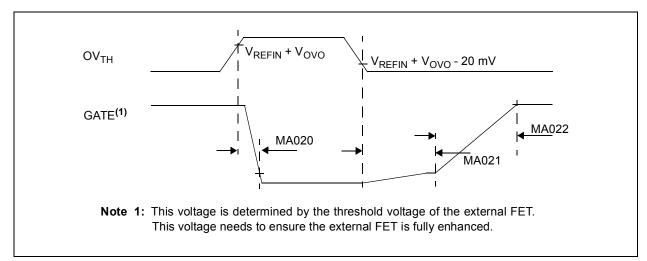

FIGURE 1-4: OV<sub>TH</sub>-to-gate Waveform.

TABLE 1-5: OV<sub>TH</sub>-TO-GATE TIMING REQUIREMENTS

| Param.<br>No. | Parameter                              | Sym                                     | Min | Тур  | Max | Units | Conditions |

|---------------|----------------------------------------|-----------------------------------------|-----|------|-----|-------|------------|

| MA020         | OV <sub>TH</sub> High to GATE Low      | T <sub>OV</sub> H2 <sub>GATE</sub> L    | _   | 58.4 | _   | μs    |            |

| MA021         | OV <sub>TH</sub> Low to GATE Fast Ramp | T <sub>OV</sub> L2 <sub>GATE</sub> FR   | _   | 40.8 | _   | μs    |            |

| MA022         | GATE Fast Ramp to GATE High            | T <sub>GATE</sub> FR2 <sub>GATE</sub> H |     | 17.8 | _   | ms    |            |

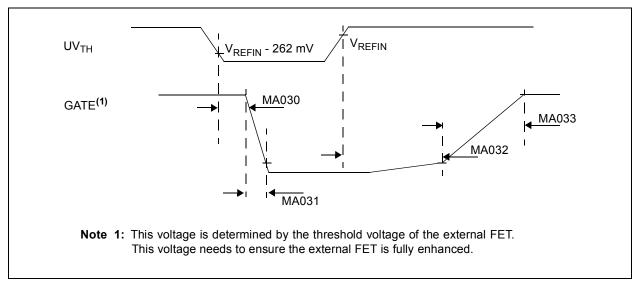

FIGURE 1-5: UV<sub>TH</sub>-to-gate Waveform

TABLE 1-6: UVTH-TO-GATE TIMING REQUIREMENTS

| Param.<br>No. | Parameter                                 | Sym                                     | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                |

|---------------|-------------------------------------------|-----------------------------------------|-----|--------------------|-----|-------|---------------------------|

| MA030         | UV <sub>TH</sub> Low to GATE Falling Edge | T <sub>UV</sub> L2 <sub>GATE</sub> F    |     | 108                |     | μs    | C <sub>UVD</sub> = 800 nF |

| MA031         | GATE High to GATE Low                     | T <sub>GATE</sub> H2 <sub>GATE</sub> L  |     | 25.8               | _   | μs    |                           |

| MA032         | ENABLE High to GATE Fast Ramp             | T <sub>UV</sub> H2 <sub>GATE</sub> FR   | _   | 40.4               | _   | ms    |                           |

| MA033         | GATE Fast Ramp to GATE High               | T <sub>GATE</sub> FR2 <sub>GATE</sub> H | _   | 58.4               | _   | ms    |                           |

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C, unless otherwise stated.

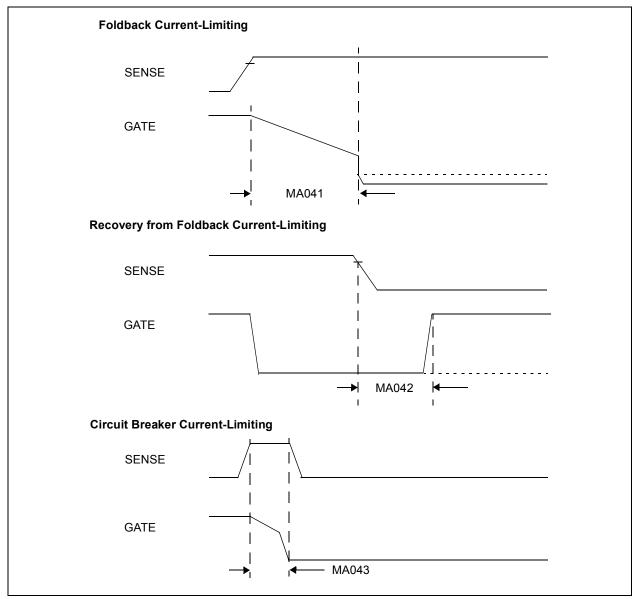

FIGURE 1-6: Sense-to-gate Waveform.

TABLE 1-7: SENSE-TO-GATE TIMING REQUIREMENTS

| Param.<br>No. | Parameter                      | Sym                                     | Min | Тур  | Max | Units | Conditions                                           |

|---------------|--------------------------------|-----------------------------------------|-----|------|-----|-------|------------------------------------------------------|

| MA041         | GATE Current Limit to GATE Off | T <sub>GATE</sub> CL2 <sub>GATE</sub> O | _   | 5.5  | _   | ms    | $C_{TIMER}$ = 0.68 µF<br>$R_{ISET}$ = 124 k $\Omega$ |

| MA042         | GATE Current Limit Recovery    | T <sub>GATE</sub> CL                    | _   | 10.2 | _   |       | $C_{TIMER}$ = 0.68 µF<br>$R_{ISET}$ = 124 k $\Omega$ |

| MA043         | SENSE High to GATE Off         | T <sub>SENSE</sub> H2 <sub>GATE</sub> O | _   | 3.6  | _   | ms    |                                                      |

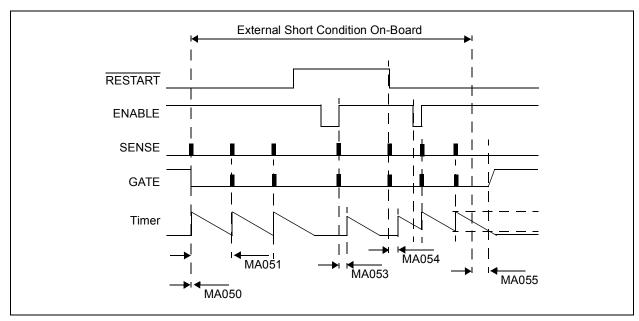

FIGURE 1-7: Current Limit Waveform.

TABLE 1-8: CURRENT LIMIT TIMING REQUIREMENTS

| Param.<br>No. | Parameter                                  | Sym                                        | Min | Тур  | Max | Units | Conditions                                             |

|---------------|--------------------------------------------|--------------------------------------------|-----|------|-----|-------|--------------------------------------------------------|

| MA050         | External Short to Timer period start       | T <sub>SHORT</sub> 2 <sub>TIMER</sub> S    | _   | 171  | _   | mS    |                                                        |

| MA051         | Timer period                               | T <sub>TIMER</sub> P                       | _   | 5.8  | _   | sec   | $C_{TIMER} = 0.68 \mu F$<br>$R_{DISCH} = 1.6 M\Omega$  |

| MA053         | ENABLE High to Timer period start          | T <sub>ENABLE</sub> H2 <sub>TIMER</sub> S  | _   | 30.5 | _   | mS    | $C_{TIMER} = 0.68 \mu F$<br>$R_{DISCH} = 1.6 M\Omega$  |

| MA054         | RESTART Low to Timer period start          | T <sub>RESTART</sub> L2 <sub>TIMER</sub> S | _   | 30.9 | _   | mS    | $C_{TIMER} = 0.68 \mu F$<br>$R_{DISCH} = 11.6 M\Omega$ |

| MA055         | External Short removed to Timer off Note 2 | T <sub>NOSHORT</sub> 2 <sub>TIMER</sub> O  | _   | 5.8  | _   | sec   | $C_{TIMER} = 0.68 \mu F$<br>$R_{DISCH} = 1.6 M\Omega$  |

**<sup>2:</sup>** This is up to one additional timer period because the external short circuit is removed asynchronously to the timer. The timer must time out before normal operation returns.

## MCP18480

NOTES:

## 2.0 DC CHARACTERISTIC CURVES

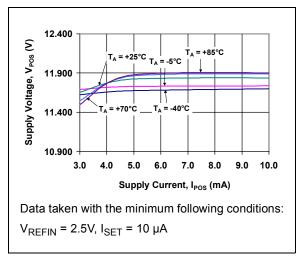

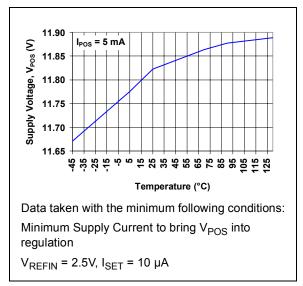

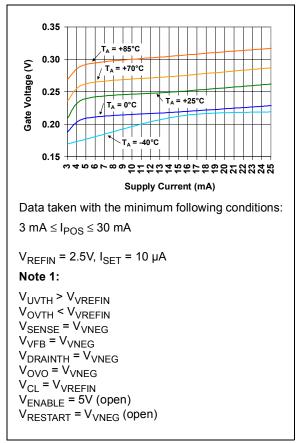

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**FIGURE 2-1:** Supply Current  $(I_{POS})$  vs. Supply Voltage  $(V_{POS})$ .

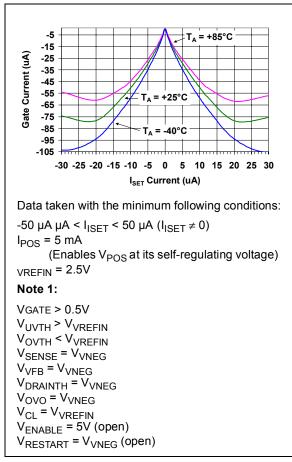

**FIGURE 2-2:** Minimum Supply Current vs. Temperature.

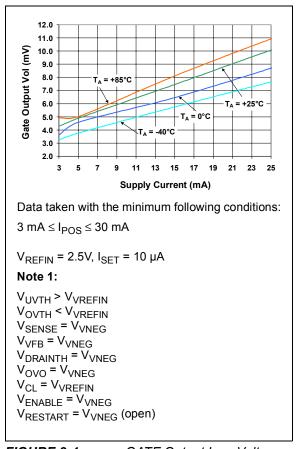

**FIGURE 2-3:** GATE Output High-Voltage  $(V_{POS}-V_{GATE})$  vs. Supply Current  $(I_{POS})$ .

**FIGURE 2-4:** GATE Output Low-Voltage  $(V_{GATE} - V_{NEG})$  vs. Supply Current  $(I_{POS})$ .

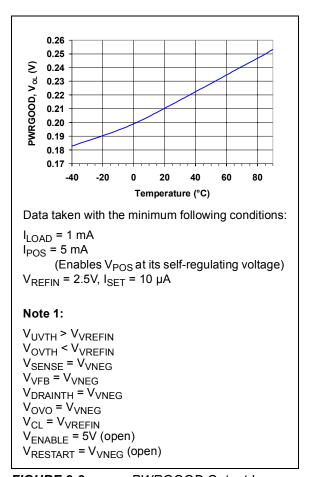

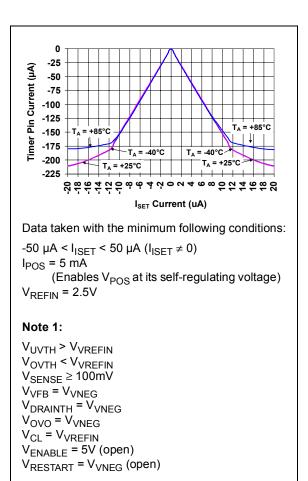

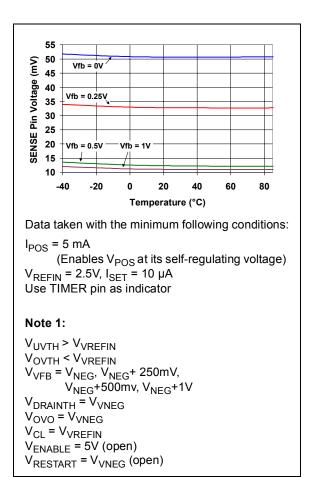

$I_{POS} = 5 \text{ mA}$

(Enables V<sub>POS</sub> at its self-regulating voltage)

$V_{REFIN}$  = 2.5V,  $I_{SET}$  = 10  $\mu A$

## Note 1:

V<sub>UVTH</sub> > V<sub>VREFIN</sub>

V<sub>OVTH</sub> < V<sub>VREFIN</sub>

$V_{SENSE} = V_{VNEG}$

$V_{VFB} = V_{VNEG}$

$V_{DRAINTH} = V_{VNEG}$  $V_{OVO} = V_{VNEG}$

V<sub>CL</sub> = V<sub>VREFIN</sub> V<sub>ENABLE</sub> = 5V (open)

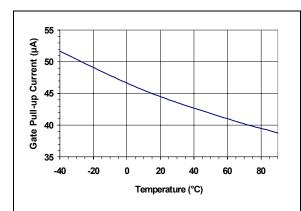

FIGURE 2-5: GATE Source (Pull-Up) Current vs. Temperature.

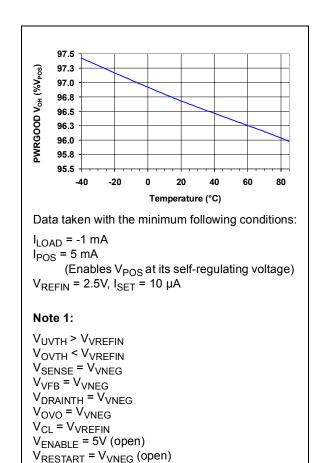

Data taken with the minimum following conditions:

$I_{POS} = 5 \text{ mA}$

(Enables V<sub>POS</sub> at its self-regulating voltage)

$V_{REFIN}$  = 2.5V,  $I_{SET}$  = 10  $\mu A$

## Note 1:

VGATE > 0.5V

V<sub>UVTH</sub> > V<sub>VREFIN</sub>

$V_{OVTH} < V_{VREFIN}$

$V_{SENSE} = V_{VNEG}$

$V_{VFB} = V_{VNEG}$

V<sub>DRAINTH</sub> = V<sub>VNEG</sub> V<sub>OVO</sub> = V<sub>VNEG</sub> V<sub>CL</sub> = V<sub>VREFIN</sub>

V<sub>ENABLE</sub> = V<sub>VNEG</sub>

$V_{RESTART} = V_{VNEG}$  (open)

FIGURE 2-6: GATE Sink (Pull-Down) Current vs. Temperature.

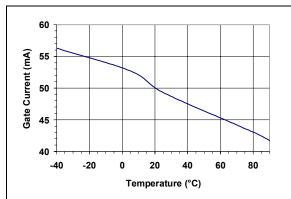

**FIGURE 2-7:** GATE Source Current vs.  $I_{SFT}$  Pin Current.

**FIGURE 2-8:** PWRGOOD Output Low Voltage ( $V_{OL}$ ) vs. Temperature.

**FIGURE 2-9:** PWRGOOD Output High-Voltage  $(V_{OH})$  vs. Temperature.

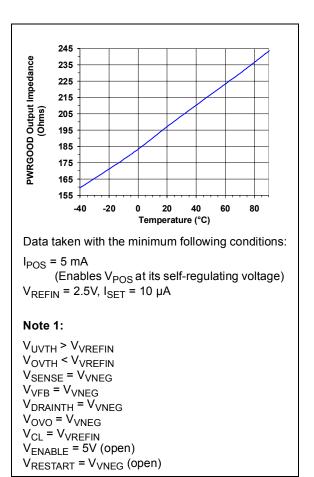

**FIGURE 2-10:** PWRGOOD Output High-Impedance vs. Temperature.

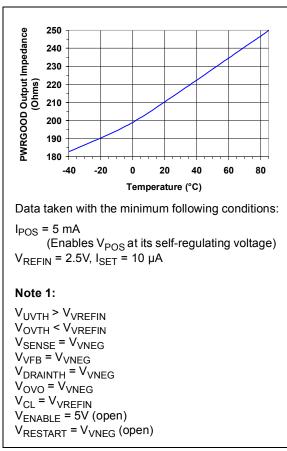

**FIGURE 2-11:** PWRGOOD Output Low-Impedance vs. Temperature.

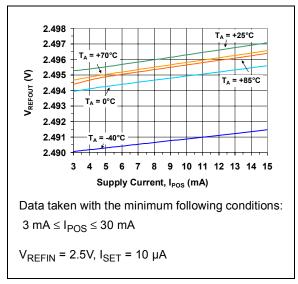

**FIGURE 2-12:**  $V_{REFOUT}$  vs. Supply Current  $(I_{POS})$ .

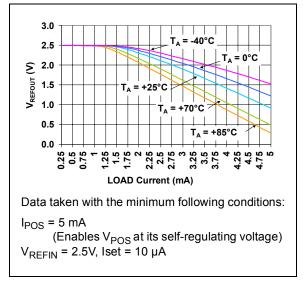

FIGURE 2-13:  $V_{REFOUT}$  vs. LOAD.

#### Note 1:

VUVTH > VVREFIN

VOVTH < VVREFIN

VSENSE = VVNEG

VVFB = VVNEG

VDRAINTH = VVNEG

VOVO = VVNEG

VCL = VVREFIN

VENABLE = 5V (open)

VRESTART = VVNEG (open)

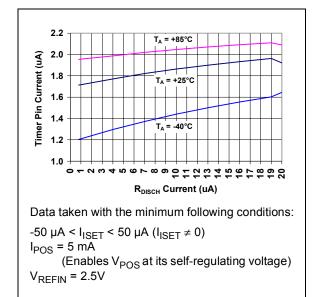

**FIGURE 2-14:** TIMER Pin Output Low Current vs. R<sub>DISCH</sub> Current.

**FIGURE 2-15:** TIMER Pin Output High Current vs. I<sub>SET</sub> Current.

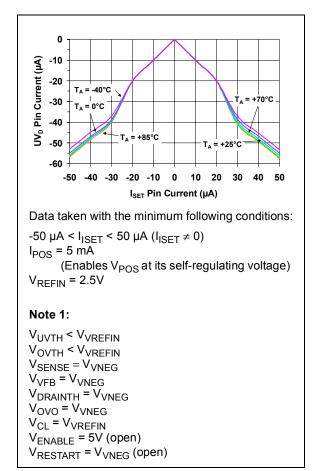

**FIGURE 2-16:**  $UV_D$  Pin Current vs.  $I_{SET}$  Pin Current.

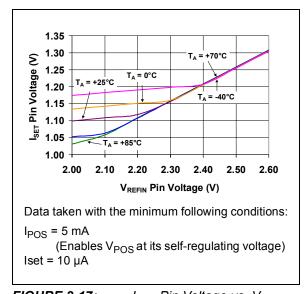

**FIGURE 2-17:**  $I_{SET}$  Pin Voltage vs.  $V_{REFIN}$  Pin Voltage.

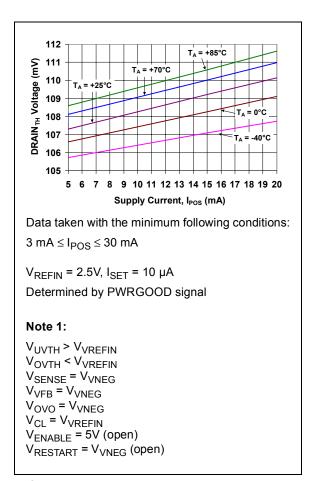

**FIGURE 2-18:** DRAINTH Threshold Voltage vs. Supply current  $(I_{POS})$ .

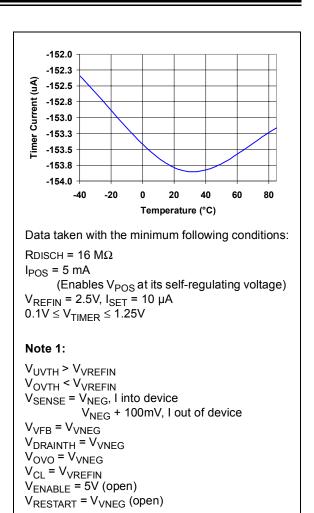

$I_{POS} = 5 \text{ mA}$

(Enables V<sub>POS</sub> at its self-regulating voltage)

$V_{REFIN}$  = 2.5V,  $I_{SET}$  = 10  $\mu A$

$R_{DISCH} = 16 M\Omega$

#### Note 1:

V<sub>UVTH</sub> > V<sub>VREFIN</sub>

$V_{OVTH} < V_{VREFIN}$

$V_{SENSE} = V_{VNEG}$   $V_{VFB} = V_{VNEG}$

V<sub>DRAINTH</sub> = V<sub>VNEG</sub>

$V_{OVO} = V_{VNEG}$

$V_{CL} = V_{VREFIN}$

$V_{ENABLE} = 5V \text{ (open)}$

$V_{RESTART} = V_{VNEG}$  (open)

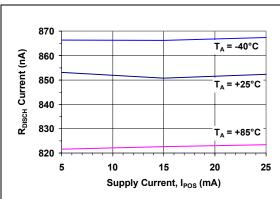

**FIGURE 2-19:** Current (I<sub>POS</sub>). R<sub>DISCH</sub> Current vs. Supply

Data taken with the minimum following conditions:

$I_{POS} = 5 \text{ mA}$

(Enables V<sub>POS</sub> at its self-regulating voltage)

$V_{REFIN}$  = 2.5V,  $I_{SET}$  = 10  $\mu$ A

$I_{RDISCH}$  from 100 nA to 10  $\mu A$  (500 nA steps)

#### Note 1:

V<sub>UVTH</sub> > V<sub>VREFIN</sub>

$V_{OVTH} < V_{VREFIN}$

$V_{SENSE} = V_{VNEG}$

$V_{VFB} = V_{VNEG}$

$V_{DRAINTH} = V_{VNEG}$

V<sub>OVO</sub> = V<sub>VNEG</sub>

$V_{CL} = V_{VREFIN}$   $V_{ENABLE} = 5V \text{ (open)}$

$V_{RESTART} = V_{VNEG}$  (open)

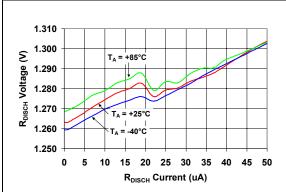

**FIGURE 2-20:** Current.

R<sub>DISCH</sub> Voltage vs. R<sub>DISCH</sub>

$I_{POS} = 5 \text{ mA}$

(Enables  $V_{POS}$  at its self-regulating voltage)

$V_{REFIN}$  = 2.5V,  $I_{SET}$  = 10  $\mu$ A

Determined by GATE voltage

### Note 1:

V<sub>UVTH</sub> > V<sub>VREFIN</sub>

$V_{OVTH} < V_{VREFIN}$

$V_{SENSE} = V_{VNEG}$   $V_{VFB} = V_{VNEG}$

$V_{DRAINTH} = V_{VNEG}$   $V_{OVO} = V_{VNEG}$

V<sub>CL</sub> = V<sub>VREFIN</sub>

$V_{RESTART} = V_{VNEG}$  (open)

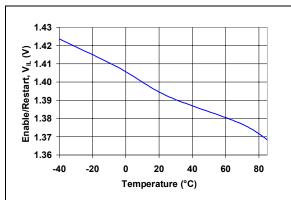

**FIGURE 2-21:** ENABLE/RESTART Pin Trip Point Voltage vs. Temperature.

**FIGURE 2-22:** TIMER Output Sink Current vs. Temperature.

FIGURE 2-23: TIMER Output Source Current vs. Temperature.

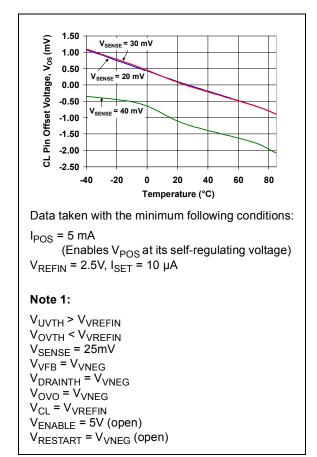

**FIGURE 2-24:** CL pin Input Offset Voltage vs. Temperature.

**FIGURE 2-25:** SENSE Pin Input Threshold vs. Temperature.

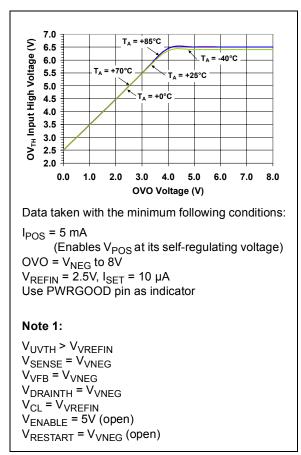

**FIGURE 2-26:** OV<sub>TH</sub> Input Rising Threshold vs. OVO Voltage.

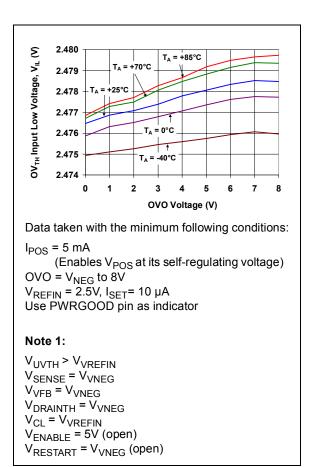

**FIGURE 2-27:** OV<sub>TH</sub> Input Falling Threshold vs. OVO Voltage.

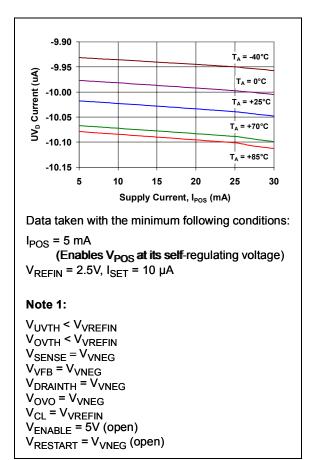

**FIGURE 2-28:** UV<sub>D</sub> Current vs. Supply Current (IPOS).

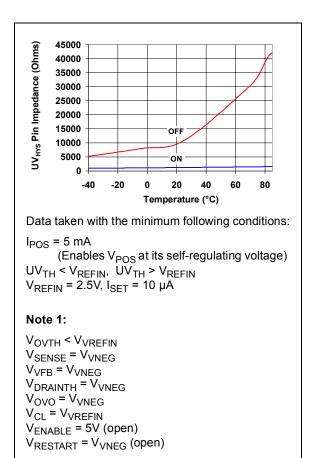

**FIGURE 2-29:**  $UV_{HYS}$  Pin Impedance vs. Temperature.

$I_{POS} = 5 \text{ mA}$

(Enables V<sub>POS</sub> at its self-regulating voltage)

$V_{REFIN}$  = 2.5V,  $I_{SET}$  = 10  $\mu A$

Use PWRGOOD pin as indicator

#### Note 1:

$V_{OVTH} < V_{VREFIN}$

V<sub>SENSE</sub> = V<sub>VNEG</sub> V<sub>VFB</sub> = V<sub>VNEG</sub> V<sub>DRAINTH</sub> = V<sub>VNEG</sub>

$V_{OVO} = V_{VNEG}$

$V_{CL} = V_{VREFIN}$

V<sub>ENABLE</sub> = 5V (open)

$V_{RESTART} = V_{VNEG}$  (open)

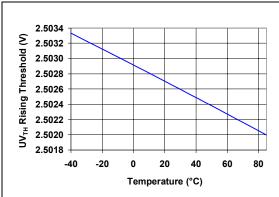

FIGURE 2-30: UV<sub>TH</sub> Input Rising

Threshold vs. Temperature.

Data taken with the minimum following conditions:

$I_{POS} = 5 \text{ mA}$

(Enables V<sub>POS</sub> at its self-regulating voltage)

$V_{REFIN}$  = 2.5V,  $I_{SET}$  = 10  $\mu A$

Use PWRGOOD pin as indicator

#### Note 1:

$V_{OVTH} < V_{VREFIN}$

$V_{SENSE} = V_{VNEG}$

$V_{VFB} = V_{VNEG}$

V<sub>DRAINTH</sub> = V<sub>VNEG</sub> V<sub>OVO</sub> = V<sub>VNEG</sub> V<sub>CL</sub> = V<sub>VREFIN</sub> V<sub>ENABLE</sub> = 5V (open)

$V_{RESTART} = V_{VNEG}$  (open)

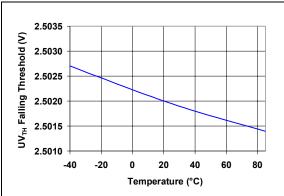

**FIGURE 2-31:** UV<sub>TH</sub> Input Falling

Threshold vs. Temperature.

$I_{POS} = 5 \text{ mA}$

(Enables V<sub>POS</sub> at its self-regulating voltage)

$V_{REFIN}$  = 2.5V,  $I_{SET}$  = 10  $\mu$ A

Use PWRGOOD pin as indicator

### Note 1:

V<sub>OVTH</sub> < V<sub>VREFIN</sub>

$V_{SENSE} = V_{VNEG}$

$V_{VFB} = V_{VNEG}$

$V_{DRAINTH} = V_{VNEG}$

$V_{OVO} = V_{VNEG}$

$V_{CL} = V_{VREFIN}$

V<sub>ENABLE</sub> = 5V (open) V<sub>RESTART</sub> = V<sub>VNEG</sub> (open)

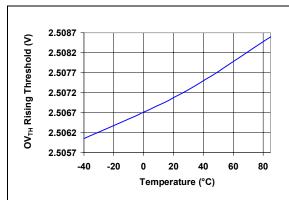

**FIGURE 2-32:** OV<sub>TH</sub> Input Rising Threshold vs. Temperature.

Data taken with the minimum following conditions:

$I_{POS} = 5 \text{ mA}$

(Enables V<sub>POS</sub> at its self-regulating voltage)

$V_{REFIN}$  = 2.5V,  $I_{SET}$  = 10  $\mu$ A

$V_{UVHYS} = V_{NEG}$

Use PWRGOOD pin as indicator

### Note 1:

$V_{OVTH} < V_{VREFIN}$

$V_{SENSE} = V_{VNEG}$

$V_{VFB} = V_{VNEG}$

$V_{DRAINTH} = V_{VNEG}$

$V_{OVO} = V_{VNEG}$

V<sub>CL</sub> = V<sub>VREFIN</sub> V<sub>ENABLE</sub> = 5V (open)

$V_{RESTART} = V_{VNEG}$  (open)

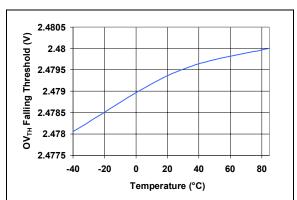

**FIGURE 2-33:** OV<sub>TH</sub> Input Falling

Threshold vs. Temperature.

## MCP18480

NOTES:

## 3.0 PIN DESCRIPTIONS

TABLE 3-1: MCP18480 PIN DESCRIPTIONS

| Pin Name          | Pin<br>Number<br>SSOP | Pin<br>Direction | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|-----------------------|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>POS</sub>  | 1                     | l                | Р              | Positive supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| . 55              |                       |                  |                | Internal Shunt Regulator connected between $V_{POS}$ and $V_{NEG}$ limits the potential to 12V between these two pins. A series resistor must be placed on the $V_{POS}$ pin to limit the current into the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OV <sub>TH</sub>  | 2                     | I                | Α              | Overvoltage protection threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                   |                       |                  |                | An external resistor divider network is connected to this input pin to program the overvoltage protection threshold. The selected external resistor values for the $OV_TH$ to system ground and $OV_TH$ to $V_NEG$ resistors should have currents in the 1 mA range. A typical Overvoltage threshold is -76V. Internal hysteresis in the overvoltage input comparator will allow proper operation once $V_NEG$ falls below the selected threshold.                                                                                                                                                                                                                                                                                                                           |

| UV <sub>TH</sub>  | 3                     | I                | Α              | Undervoltage lockout threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                       |                  |                | An external resistor divider network is connected to this input pin to program the undervoltage lockout threshold. If the voltage on $\rm UV_{TH}$ is less than $\rm V_{NEG}$ + 2.5V, the undervoltage comparator will trip, indicating an Undervoltage condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                       |                  |                | An external hysteresis resistor can be used to set the high-to-low ( $V_{THF}$ ) threshold below the low-to-high ( $V_{THR}$ ) threshold. For telecom network equipment, it is desirable to have shutdown occur at -38.5V and the startup set at -43.0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| UV <sub>HYS</sub> | 4                     | I                | Α              | Undervoltage internal comparator hysteresis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   |                       |                  |                | An external resistor is connected between this input to the $\rm UV_{TH}$ input pin to adjust the hysteresis of the internal Undervoltage comparator. Since it is desirable to shut down at -38.5V and restart at -43.0V in telecom switch equipment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UV <sub>D</sub>   | 5                     | I/O              | Α              | Undervoltage event delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   |                       |                  |                | An external capacitor is connected to this input pin to set the delay between when the UV $_{TH}$ pin drops below the trip point specified by the voltage on the V $_{REFIN}$ pin and when the system shutdown occurs (causing the PWRGOOD pin to be driven to an inactive level and the GATE pin to be pulled to the V $_{NEG}$ pin voltage level). The UV $_{D}$ pin sources a current equivalent to the I $_{ISET}$ (in typical applications, the I $_{ISET}$ current equals 10 µA), which charges this external capacitor while an internal comparator compares this voltage on the UV $_{D}$ pin to $ V_{REFIN} /2$ . Typically, for telecom equipment, the system is expected to shut down when the input voltage falls below -38.5V ( $\pm$ 1.0V DC) for greater than |

|                   |                       |                  |                | 100 ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input O = Output

P = Power CMOS = CMOS-compatible input

A = Analog D = Digital

TABLE 3-1: MCP18480 PIN DESCRIPTIONS (CONTINUED)

| Pin Name            | Pin<br>Number<br>SSOP | Pin<br>Direction | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|-----------------------|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>REFOUT</sub> | 6                     | 0                | Α              | Reference output.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                     |                       |                  |                | Internal reference output voltage (typically 2.5V). Usually tied back to the $V_{\sf REFIN}$ pin unless an external high-precision reference voltage is desired.                                                                                                                                                                                                                                                                                                            |

| V <sub>REFIN</sub>  | 7                     | I                | Α              | Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     |                       |                  |                | This pin allows a high-precision reference voltage for the following functions:                                                                                                                                                                                                                                                                                                                                                                                             |

|                     |                       |                  |                | Undervoltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                     |                       |                  |                | Overvoltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                     |                       |                  |                | DRAIN Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     |                       |                  |                | Current Limit Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     |                       |                  |                | If the precision of the $V_{REFOUT}$ output voltage is acceptable, tie the $V_{REFOUT}$ pin to the $V_{REFIN}$ pin.                                                                                                                                                                                                                                                                                                                                                         |

| CL                  | 8                     | I                | Α              | Current Limit.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     |                       |                  |                | Input used to set the maximum current limit threshold allowed by the system via a resistor divider network (with the resistor $R_{CL1}$ between the $V_{REFIN}$ pin and the CL pin and resistor $R_{CL}$ between the $V_{NEG}$ pin and the CL pin). If the voltage across the sense resistor exceeds the voltage on the CL pin, it implies that there is excessive current over the allowed limit and forces the GATE pin to the $V_{NEG}$ pin voltage level without delay. |

| I <sub>SET</sub>    | 9                     | I                | Α              | Current source set.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     |                       |                  |                | Establishes the internal I <sub>SOURCE</sub> for the following:                                                                                                                                                                                                                                                                                                                                                                                                             |

|                     |                       |                  |                | Undervoltage Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     |                       |                  |                | Current Limit Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     |                       |                  |                | GATE Pin Source Current                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                     |                       |                  |                | An external resistor $R_{ISET}$ from the $I_{SET}$ pin must be connected to either the $V_{NEG}$ pin or the $V_{REFIN}$ pin to set $I_{BIAS}$ , which will then establish the current sources throughout the device. The $I_{BIAS}$ current is the same for either connection.                                                                                                                                                                                              |

|                     |                       |                  |                | Connecting the $R_{\rm ISET}$ resistor to the $V_{\rm NEG}$ pin will establish the PWRGOOD pin output polarity to be active-high. Connecting the $R_{\rm ISET}$ resistor to the $V_{\rm REFIN}$ pin will establish the PWRGOOD pin output polarity to be active-low.                                                                                                                                                                                                        |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

O = Output

P = Power

CMOS = CMOS-compatible input

A = Analog

D = Digital

TABLE 3-1: MCP18480 PIN DESCRIPTIONS (CONTINUED)

| Pin Name           | Pin<br>Number | Pin<br>Direction | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------|---------------|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TIMED              | SSOP          |                  |                | Owner this is Trans                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| TIMER              | 10            | I                | Α              | Current Limit Timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                    |               |                  |                | The value of the external capacitor ( $C_{\text{TIMER}}$ ) connected to the TIMER pin sets the two time periods used during a current-limit event. These are:                                                                                                                                                                                                                                                                                                                |  |

|                    |               |                  |                | The time that the GATE pin will limit the current through the external FET                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                    |               |                  |                | The time that the GATE pin will disable the external FET                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                    |               |                  |                | During current limit, a pull-up current source charges up the external capacitor. Until the voltage on the TIMER pin reaches $V_{REFIN}/2$ , the GATE pin is driven to maintain a reduced current flow determined by the $V_{DS}$ of the external FET.                                                                                                                                                                                                                       |  |

|                    |               |                  |                | While the capacitor is being discharged by the pull-down current (pull-up current is off), the GATE pin is at V <sub>NEG</sub> and the PWRGOOD pin is deasserted. When the TIMER voltage falls below approximately 100 mV, the GATE pin turns on, if the RESTART pin is low, to reset the internal fault latch. If the RESTART pin is high, the GATE pin remains off until the ENABLE pin is forced low. It is then forced high or the RESTART pin is forced low (asserted). |  |

|                    |               |                  |                | The PWRGOOD pin reasserts after the voltages on the DRAIN <sub>TH</sub> and GATE pins meet the appropriate conditions.                                                                                                                                                                                                                                                                                                                                                       |  |

|                    |               |                  |                | The TIMER pin pull-up current is proportioned to the $I_{\rm ISET}$ current (approximately a multiple of 16).                                                                                                                                                                                                                                                                                                                                                                |  |

| $V_{NEG}$          | 11            | I                | Р              | Negative supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                    |               |                  |                | The negative voltage applied to the board by the backplane (typically the most negative voltage in the system).                                                                                                                                                                                                                                                                                                                                                              |  |

| R <sub>DISCH</sub> | 12            | I                | Α              | External MOSFET activation delay.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                    |               |                  |                | An external resistor ( $R_{RDISCH}$ ) is connected between the $R_{DISCH}$ pin and the $V_{NEG}$ pin and is used to set the delay between the deactivation and activation of the external pass MOSFET during a current-limit event. The delay is set by the values of the external capacitor ( $C_{TIMER}$ ) and the external resistor ( $R_{RDISCH}$ ). The formulas are: $T_{DEACT} = (C_{TIMER} \times R_{ISET}) / 16$                                                    |  |

|                    |               |                  |                | $T_{ACT} = (9.2 \times R_{RDISCH} \times C_{TIMER})$                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

Legend: TTL = TTL compatible input

P = Power

ST = Schmitt Trigger input with CMOS levels

I = Input O = Output

CMOS = CMOS-compatible input

A = Analog D = Digital

TABLE 3-1: MCP18480 PIN DESCRIPTIONS (CONTINUED)

| Pin Name            | Pin<br>Number<br>SSOP | Pin<br>Direction | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|---------------------|-----------------------|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SENSE               | 13                    | I                | Α              | Over-current sense.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     |                       |                  |                | The voltage on the SENSE input pin is used to detect over-current conditions in the load connected to the external MOSFET. This pin is directly connected to the source of the MOSFET, with an external resistor (R_SENSE) (typically a low resistance) connected between the source of the MOSFET and $V_{NEG}$ .                                                                                                                                                                                                                                                                                                                                  |  |

| GATE                | 14                    | 0                | Α              | MOSFET gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     |                       |                  |                | The GATE output pin attaches to the gate of the external MOSFET. The voltage on the GATE pin is pulled to the voltage on the $V_{NEG}$ pin whenever the voltage on the UV $_{TH}$ pin is less than the voltage on the $V_{REFIN}$ pin, or the voltage on the $V_{TH}$ pin is greater than the voltage on the $V_{REFIN}$ pin.                                                                                                                                                                                                                                                                                                                       |  |

|                     |                       |                  |                | The GATE pin is also pulled to the voltage on the $V_{NEG}$ pin when the ENABLE input pin is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                     |                       |                  |                | When current limit is reached, the voltage on the GATE pin is adjusted to maintain a constant voltage across the $R_{SENSE}$ resistor while the $C_{TIMER}$ capacitor starts to charge. When the voltage on $C_{TIMER}$ exceeds $V_{REFIN}/2$ , the GATE pin is pulled to $V_{NEG}$ to turn off the external MOSFET. A RC network can be added from the GATE pin to the drain of the external MOSFET, along with a capacitor from the GATE pin to the $V_{NEG}$ pin, to control the slew rate of the GATE pin.                                                                                                                                      |  |

|                     |                       |                  |                | The GATE pin pull-up current is proportioned to the I <sub>ISET</sub> current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| $V_{FB}$            | 15                    | I                | Α              | External MOSFET drain monitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |